|

Т»Ј©ёЕКц

ёГїОМвФґУЪ±ѕІ©КїµгНЁ№эНвРєПЧчХл¶ФЧ°±ёїХѕьµДї№ёЙИЕµзМЁіцїЪРНЅшРРёДФмЙијЖµДЧЁПоїОМвЈ¬Дї±кОЄМṩһЦЦїЙ±аіМЕдЦГµДї№ёЙИЕµзМЁЈ¬ДЬ№»ёщѕЭРиТЄ¶Фµ±З°ОТїХѕьЧ°±ёµДДіРНі¬¶МІЁї№ёЙИЕµзМЁЅшРРРФДЬЦё±кµДЛх·ЕїШЦЖЈ¬ТФККУ¦іцїЪРНєЕµДРиТЄЎЈЦчТЄДЪИЭ°ьАЁЅУКХ»ъєЛРДЛг·ЁµДёДЅшЈ¬¶ФА©ЖµВлµДВлі¤їЙЕдЦГЈ¬ТФј°¶ФУ¦І»Н¬Влі¤єНВлРтБРµДПа№ШЖчµДЙијЖєНІОКэЕдЦГ·ЅКЅµДЙијЖЎЈЅУКХ»ъОЄКэЧЦЦРЖµИнјюЅУКХ»ъЈ¬їЙФЪµҐЖ¬FPGAЙПКµПЦБЛКэЧЦЦРЖµРЕєЕЅвµчЛг·ЁТФј°КэѕЭКдИлКдіцЅУїЪµДИ«Ії№¦ДЬЎЈ

¶юЈ©№¤ЧчФАн

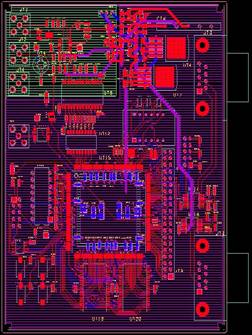

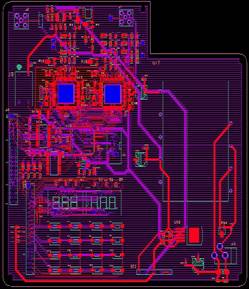

ИнјюА©ЖµЅУКХ»ъ°ьє¬ЙдЖµЗ°¶ЛЈ¬ЖµВКєПіЙЖчЈ¬КэЧЦЦРЖµДЈїйТФј°µзФґДЈїйЈ¬ёЁЦъµчКФДЈїйµИЖдЛыНвО§µзВ·ЎЈ

±ѕїОМвєЛРДІї·ЦОЄїЙБй»оЕдЦГµДКэЧЦЦРЖµРЕєЕґ¦АнДЈїйЈ¬Ѕ«УГУЪМж»»ПЦЧ°µДї№ёЙИЕµзМЁЦРЖµґ¦АнµҐФЄЈ¬¶юХЯЅУїЪµД»ъРµєНµзЖчМШРФЅ«±ЈіЦТ»ЦВТФЦ§іЦЦ±ЅУДЈїйМж»»ЎЈЖдЛыДЈїйЦчТЄУГУЪСР·ўЅЧ¶ОЅшРРЧФЦчµчКФєНСйЦ¤µИУГНѕЎЈ

ИэЈ©ИнјюА©ЖµКХ»ъМШµг

1Ј© µҐРѕЖ¬ЦРЖµРЕєЕґ¦АнµҐФЄ

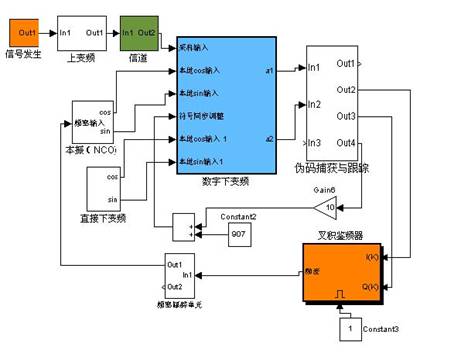

ФЪµҐЖ¬FPGAЈЁAltera№«ЛѕµДCycloneПµБР EP1C12Ј©ЦРКµПЦБЛКэЧЦЦРЖµBPSK/DSРЕєЕНкХыµД·ўЙдєНЅУКХ№эіМЎЈ

2Ј©ІЙУГ·Ц¶ОКэЧЦЖҐЕдВЛІЁЖчКµПЦРЕєЕЅвА©

Ц±А©РЕєЕЅвА©ІЙУГ·Ц¶ОКЅЖҐЕдВЛІЁЖчРОКЅµДПа№ШЖчЈ¬ЧоґуВлі¤128Ј¬ЗТВлі¤їЙ±дЎЈ¶ФЖҐЕдВЛІЁЖчµДУІјюКµПЦЅшРРБЛЧКФґУЕ»ЇЈ¬ЕдєПХЫµюКЅµДПа№ШЖчЅб№№Ј¬ХјУГµДУІјюЧКФґ±ИЦ±ЅУКµПЦ·ЅКЅґуґујхРЎЎЈ

3Ј©»щУЪSOPCјјКх·Ѕ°ёЈ¬їЙА©Х№КµПЦИнјюА©ЖµЅУКХ»ъ

ФЪFPGAЦРјЇіЙAlteraµДИнєЛґ¦АнЖчЈ¬ЕдєПЖдИнјюЦёБо¶ЁЦЖ№¦ДЬєНЖдЛыїЙУГIPЧКФґЈ¬№№ЅЁБЛТ»ёцИнјюА©ЖµЅУКХ»ъµДЖЅМЁЎЈ

4Ј©УµУРНкХыµДЛг·ЁєНИнУІјюЧКФґЈ¬ККУ¦І»Н¬У¦УГРиЗуЎЈ

»щУЪ·Ц¶ОКЅЖҐЕдВЛІЁЖчµДРЕєЕЅвµчЛг·ЁїЙТФЦ§іЦёЯ¶ЇМ¬РЕєЕµДЅУКХЈ¬МṩБЛ¶ЇМ¬МхјюПВ¶АМШµДОЮ·мЗР»»µДЛшЖµ»·В·їШЦЖЛг·ЁЈ¬К№µГФШІЁ»ЦёґёьОЄїмЅЭЎўЖЅОИЎЈґЛНвЈ¬»№ѕЯ±ёНкХыµДMatlab·ВХжДЈРНЈ¬VerilogУІјю·ВХжДЈРНєНТФFPGA°еОЄЦРРДУІјюІвКФЖЅМЁЈ¬їЙЧчОЄµЪИэ·ЅУГАґСР·ўА©ЖµНЁРЕІъЖ·µДІОїјЖЅМЁЎЈ

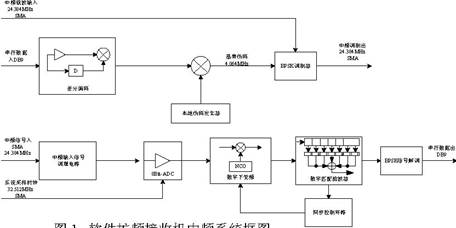

Нј1. ИнјюА©ЖµЅУКХ»ъЦРЖµПµНіїтНј

ЛДЈ©ЦчТЄјјКхЦё±к

»щґшКэѕЭµчЦЖ·ЅКЅЈєDBPSK\QPSK

»щґшКэѕЭґ«КдЛЩВКЈє32\64\128kb/s

Ц±А©А©ЖµВлЈє128О»µДMРтБРЈЁВлРНїЙСЎЈ©Ј»

Ц±А©О±ВлЛЩВКЈє4.096Mb/s

»щґшіЙРОВціеЈє№цЅµПµКэїЙµчµДЙэУаПТВціеЈ»

ЦРЖµЖµВКЈє24.384MHzЈЁїЙСЎЈ©Ј»

ЦРЖµРЕПўґшїнЈєґуУЪ8MHzЈ»

ЦРЖµКдИлРЕФл±ИЈє0dB~-5dB

¶аЖХАХЖµТЖЈєІ»РЎУЪ40KHzЈ»

Н¬ІЅК±јдЈєІ»ґуУЪ50msЈЁО±ВлІ¶»сК±јдОЄ1ёц·ыєЕЖЪЈ©

ОеЈ©У¦УГЗ°ѕ°

±ѕДЈїйКЗї№ёЙИЕµзМЁµДєЛРД№¦ДЬДЈїйЈ¬їЙ±ді¤¶ИµДА©ЖµВлі¤¶ФУ¦УЪїЙТФІ»Н¬ј¶±рµДї№ёЙИЕНЁРЕДЬБ¦Ј¬ХвТ»МШµгК№Йи±ёїЙТФёщѕЭУ¦УГ»·ѕіµДТЄЗуЈ¬ЙиЦГПаУ¦і¤¶ИµДА©ЖµВлєНВлРНЈ¬¶шОЮРиёД¶ЇµзМЁµДУІјюІї·ЦЈ¬ИГТ»ёцРНєЕµДµзМЁїЙТФККУ¦¶аЦЦІ»Н¬ТЄЗуµДУ¦УГ»·ѕіµДТЄЗуЎЈ

КэЧЦЦРЖµРЕєЕґ¦АнДЈїйµДЕдЦГБй»оРФЈ¬їЙТФ№г·єУ¦УГУЪ¶аЦЦН»·ўКЅУпТфЎўКэѕЭёЯ¶ЇМ¬ОЮПЯНЁРЕіЎєПТФј°GPSРЕєЕЅУКХ»ъЙијЖЎЈ

|